#### Rev C1, Page 1/20

#### FEATURES

- Real-time tracking, no-missing-code interpolation to 200 kHz input frequency (up to x5, to 20 kHz for x50)

- Selectable interpol. factors: x1, x2, x4, x5, x10, x20, x25, x50

- Excellent accuracy (typ. 0.6 LSB) and repeatability (typ. 0.1 LSB)

- Differential PGA inputs with selectable input resistance for voltage and current signals

- Adjustable signal conditioning for offset, amplitude, phase

- Unique signal and calibration stabilization feature: supply of encoder LED or MR bridge via controlled 40 mA current source

- Fail-safe RS422 encoder quadrature outputs with index signal

- Adjustable index position and length (from 1/4 to 1 T)

- Preselectable minimum phase distance supports fail-safe counting

- Clipping, loss-of-signal and loss-of-tracking indication

- Setup via serial EEPROM interface

- Sub-system power switch offers reverse polarity protection for the overall system

- ♦ Single 5 V supply, operation from -25(40) °C to +100(125) °C

# PACKAGES

APPLICATIONS

Rotary encoders

Linear encoders

sensors

Optical and magnetic position

Copyright © 2008 iC-Haus

Rev C1, Page 2/20

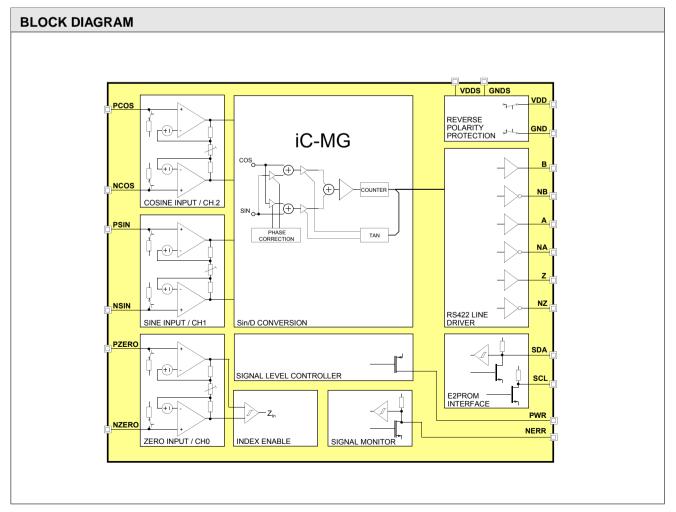

#### DESCRIPTION

Interpolator iC-MG is a non-linear A/D converter which, by applying a count-safe vector principle, digitizes sine/cosine sensor signals with selectable resolution and hysteresis. The angle value is output incrementally via differential RS422 drivers as an encoder quadrature signal with an index pulse. The minimum phase distance can be preselected, thus generating fail-safe counter signals and enhancing the noise immunity of the sensor system.

Programmable instrumentation amplifiers with selectable gain levels permit differential (in VDIFF or IDIFF mode) or single-ended input signals (in VREF or IREF mode). The modes of operation differentiate between high impedance (V modes) and low impedance (I modes). This adaptation of the iC to voltage or current signals enables MR sensor bridges or photosensors to be directly connected up to the device. The integrated signal conditioning unit allows signal amplitudes and offset voltages to be calibrated and also any phase error between the sine and cosine signals to be corrected.

For the purpose of signal stabilization (to minimize the effects of temperature and aging), the conditioned signals are fed into the power supply controller which drives the transmitting LED of optical systems via the integrated 40 mA driver stage (output PWR). If MR sensors are connected this driver stage also powers the measuring bridges. If the control thresholds are reached this is signaled at alarm message output NERR (signal loss due to wire breakage, short circuiting, dirt or aging, for example).

iC-MG is protected against a reversed power supply voltage; the integrated supply switch for loads of up to 20 mA extends this protection to cover the overall system. The device is configured via an external EEPROM.

#### PACKAGES

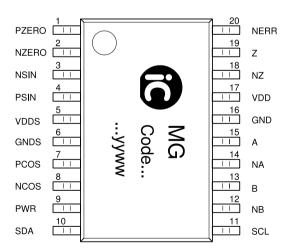

#### PIN CONFIGURATION TSSOP20

#### PIN FUNCTIONS No. Name Function

|                                                                                                    | Input Zero Signal +<br>Input Zero Signal -<br>Input Sine Signal -<br>Input Sine Signal +<br>Subsystem Positive Supply Output<br>Subsystem Ground Output<br>Input Cosine Signal +<br>Input Cosine Signal -<br>Controlled Power Supply Output (High-                                                                                                                    |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 SDA<br>11 SCL<br>12 NB<br>13 B<br>14 NA<br>15 A<br>16 GND<br>17 VDD<br>18 NZ<br>19 Z<br>20 NERR | Side)<br>Serial E2PROM Interface, data line<br>Serial E2PROM Interface, clock line<br>Incremental Output B-<br>Incremental Output B+<br>Incremental Output A-<br>Incremental Output A-<br>Ground<br>+4.3 5.5 V Supply Voltage<br>Incremental Index Output Z-<br>Incremental Index Output Z+<br>Alarm Message and Test Signal Output<br>(e.g. index enable signal Zin) |

Rev C1, Page 3/20

### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol | Parameter                                                       | Conditions                                    |      |              | Unit   |

|------|--------|-----------------------------------------------------------------|-----------------------------------------------|------|--------------|--------|

| No.  | -      |                                                                 |                                               | Min. | Max.         |        |

| G001 | V()    | Voltage at VDD, A, NA, B, NB, Z, NZ,<br>SCL, SDA, PWR           |                                               | -6   | 6            | V      |

| G002 | V()    | Voltage at NERR                                                 |                                               | -6   | 8            | V      |

| G003 | V()    | Voltage Pin vs. Pin                                             |                                               |      | 6            | V      |

| G004 | V()    | Voltage at PSIN, NSIN, PCOS, NCOS, PZERO, NZERO, SCL, SDA       |                                               | -0.3 | VDDS<br>+0.3 | V<br>V |

| G005 | I(VDD) | Current in VDD                                                  |                                               | -20  | 400          | mA     |

| G006 | I()    | Current in VDDS, GNDS                                           |                                               | -50  | 50           | mA     |

| G007 | I()    | Current in PSIN, NSIN, PCOS, NCOS, PZERO, NZERO, SCL, SDA, NERR |                                               | -20  | 20           | mA     |

| G008 | I()    | Current in A, NA, B, NB, Z, NZ                                  |                                               | -100 | 100          | mA     |

| G009 | I(PWR) | Current in PWR                                                  |                                               | -100 | 20           | mA     |

| G010 | Vd()   | ESD Susceptibility at all pins                                  | HBM, 100 pF discharged through $1.5  k\Omega$ |      | 2            | kV     |

| G011 | Tj     | Operating Junction Temperature                                  |                                               | -40  | 150          | °C     |

| G012 | Ts     | Storage Temperature Range                                       |                                               | -40  | 150          | °C     |

#### THERMAL DATA

| ltem | Symbol | Parameter                                                                                          | Conditions |      |      |      | Unit |

|------|--------|----------------------------------------------------------------------------------------------------|------------|------|------|------|------|

| No.  | -      |                                                                                                    |            | Min. | Тур. | Max. |      |

| T01  |        | Operating Ambient Temperature Range<br>(extended temperature range of -40 to<br>125 °C on request) |            | -25  |      | 100  | °C   |

Rev C1, Page 4/20

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol        | Parameter                                                                       | Conditions                                                                                      | Min.       | Тур.                          | Max.          | Unit                              |

|-------------|---------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|-------------------------------|---------------|-----------------------------------|

| Gene        | ral           |                                                                                 |                                                                                                 | IVIIII.    | тур.                          | Widx.         |                                   |

| 001         | V(VDD)        | Permissible Supply Voltage                                                      |                                                                                                 | 4.5        |                               | 5.5           | V                                 |

| 002         | I(VDD)        | Supply Current in VDD                                                           | T <sub>j</sub> = -40125 °C, no load                                                             |            |                               | 25            | mA                                |

|             |               |                                                                                 | T <sub>j</sub> = 27 °C, no load                                                                 |            | 12                            |               | mA                                |

| 003         | I(VDDS)       | Permissible VDDS Load Current                                                   |                                                                                                 | -20        |                               | 0             | mA                                |

| 004         | VDDon         | Turn-on Threshold VDD                                                           |                                                                                                 | 3.6        | 4.0                           | 4.3           | V                                 |

| 005         | VDDoff        | Turn-off Threshold VDD                                                          |                                                                                                 | 3.0        | 3.5                           | 3.8           | V                                 |

| 006         | VDDhys        | Turn-on Threshold Hysteresis                                                    |                                                                                                 | 0.4        |                               |               | V                                 |

| 007         | Vc()hi        | Clamp Voltage hi at inputs PSIN,<br>NSIN, PCOS, NCOS, PZERO,<br>NZERO, SCL, SDA |                                                                                                 | 0.3        |                               | 1.2           | V                                 |

| 008         | Vc()hi        | Clamp Voltage hi at all pins                                                    |                                                                                                 |            |                               | 11            | V                                 |

| 009         | VC()lo        | Clamp Voltage lo at all pins                                                    |                                                                                                 | -1.2       |                               | -0.3          | V                                 |

| Inputs      | s and Signal  | Conditioning: PSIN, NSIN, PCO                                                   | S, NCOS, PZERO, NZERO                                                                           |            |                               |               |                                   |

| 101         | Vin()sig      | Permissible Input Voltage Range                                                 | RSC, RZ = 0x1                                                                                   | 0.75       |                               | VDDS -<br>1.5 | V                                 |

|             |               |                                                                                 | RSC, RZ = 0x9                                                                                   | 0          |                               | VDDS          | V                                 |

| 102         | lin()sig      | Permissible Input Current Range                                                 | RSC(0), RZ(0) = 0, BIASSC = 0<br>RSC(0), RZ(0) = 0, BIASSC = 1                                  | -300<br>10 |                               | -10<br>300    | μΑ<br>μΑ                          |

| 103         | lin()         | Input Current                                                                   | RSC, RZ = 0x1                                                                                   | -10        |                               | 10            | μA                                |

| 104         | Rin()         | Input Resistance vs. VREFin()                                                   | Nominal values following Table 9                                                                | 70         | 100                           | 130           | %                                 |

| 105         | TCRin()       | Input Resistance Temperature<br>Coefficient                                     |                                                                                                 |            | 0.15                          |               | %/K                               |

| 106         | VREFin()      | Input Reference Voltage                                                         | No load, nominal values following Table 10                                                      | 90         | 100                           | 110           | %                                 |

| 107         | G             | Gain Factor (Coarse x Fine)                                                     | RSC(3), RZ(3) = 0, GRx = 0x0, GFx = 0x00<br>RSC(3), RZ(3) = 0, GRx = 0x7, GFx = max.            |            | 2<br>100                      |               |                                   |

| 108         | G-LSB         | Least Significant Gain Factor Cal.<br>Step                                      | Sine channel<br>Cosine channel<br>Zero channel                                                  |            | 1.015<br>1.06<br>1.06         |               |                                   |

| 109         | G-INL         | Integral Non-Linearity of Gain<br>Factor Cal.                                   |                                                                                                 | -1         |                               | 1             | LSB                               |

| 110         | GR-CR         | S/C-Chan. Gain Ratio Calibration Range                                          | GFC = 0x10, GFS = 0x000xFF                                                                      | 39         |                               | 255           | %                                 |

| 111         | Vin()diff     | Recommended Diff. Input Signal Level                                            | Vin()diff = V(PCHx) - V(NCHx);<br>RSC, RZ $\neq$ 0x9<br>RSC, RZ = 0x9                           | 10<br>40   |                               | 500<br>2000   | mVpp<br>mVpp                      |

| 112         | Vin()os       | Input Offset Voltage                                                            | Referenced to side of input pins                                                                |            | 25                            |               | μV                                |

| 113         |               | S/C Offset Calibration Range                                                    | Referenced to source VOSSC;<br>ORS, ORC = 00<br>ORS, ORC = 01<br>ORS, ORC = 10<br>ORS, ORC = 11 |            | ±100<br>±200<br>±600<br>±1200 |               | ·<br>%V()<br>%V()<br>%V()<br>%V() |

| 114         | OFS/C-<br>LSB | Least Significant S/C-Offset Cal.<br>Step                                       | Referenced to source VOSSC; ORS, ORC= 00                                                        |            | 0.79                          |               | %                                 |

| 115         | OFZ-LSB       | Least Significant Z-Offset Cal.<br>Step                                         | Referenced to VOSZ; ORZ = 00                                                                    |            | 3.2                           |               | %                                 |

| 116         | OFx-INL       | Integral Non-Linearity of Offset Cal.                                           |                                                                                                 | -5         |                               | 5             | LSB                               |

| 117         | PH-CR         | S/C Phase Calibration Range                                                     |                                                                                                 |            | ±20                           |               | 0                                 |

| 118         | PH-LSB        | Least Significant S/C Phase Cal.<br>Step                                        |                                                                                                 |            | 0.63                          |               | 0                                 |

| 119         | PH-INL        | Integral Non-Linearity of S/C<br>Phase Cal.                                     |                                                                                                 | -0.8       |                               | 0.8           | 0                                 |

| 120         | fin()max      | Permissible Max. Inp. Frequency                                                 |                                                                                                 | 200        |                               |               | kHz                               |

Rev C1, Page 5/20

## **ELECTRICAL CHARACTERISTICS**

| Operating Conditions: VDD = $4.55.5$ V, T <sub>i</sub> = $-40$ °C125 °C, IBN calibrated to 200 $\mu$ A, unless otherwise | e noted. |

|--------------------------------------------------------------------------------------------------------------------------|----------|

|--------------------------------------------------------------------------------------------------------------------------|----------|

| ltem<br>No. | Symbol       | Parameter                                            | Conditions                                                                                                                                               | Min.                      | Тур. | Max.                   | Unit                 |

|-------------|--------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------------|----------------------|

| Sine-t      | to-Digital C | onversion                                            |                                                                                                                                                          |                           |      |                        |                      |

| 201         | AAabs        | Absolute Angle Accuracy (follow-<br>ing calibration) | Referred to 360 deg input signal, ideal and quasi-stable input signals, SELHYS = 0                                                                       |                           | 1    | 2                      | 0                    |

| 202         | AArel        | Relative Angle Accuracy                              | Referred to A/B output period, ideal and quasi-<br>stable input signals                                                                                  | -10                       |      | +10                    | %                    |

| 203         | AAR          | Absolute Angle Repeatability                         | See 201; VDD = const., Tj = const.                                                                                                                       |                           | 0.2  |                        | 0                    |

| Outpu       | ut Line Driv | ers: A, NA, B, NB, Z, NZ                             |                                                                                                                                                          |                           |      |                        |                      |

| 501         | Vs()hi       | Saturation Voltage hi                                | Vs() = VDD - V(); I() = -20 mA                                                                                                                           |                           |      | 400                    | mV                   |

| 502         | Vs()lo       | Saturation Voltage lo                                | I() = 20 mA                                                                                                                                              |                           |      | 400                    | mV                   |

| 503         | lsc()hi      | Short-Circuit Current hi                             |                                                                                                                                                          | -60                       | -40  | -20                    | mA                   |

| 504         | lsc()lo      | Short-Circuit Current lo                             |                                                                                                                                                          | 20                        | 40   | 60                     | mA                   |

| 505         | llk()tri     | Tristate Leakage Current                             | TRIHL(1:0) = 11                                                                                                                                          |                           | 20   | 100                    | μA                   |

| 506         | tr()         | Rise Time hi                                         | RL = $100 \Omega$ to GNDS;<br>SSR(1:0) = 01<br>SSR(1:0) = 10                                                                                             | 5<br>20                   |      | 40<br>140              | ns<br>ns             |

| 507         | tf()         | Rise Time lo                                         | RL = 100 Ω to VDD;<br>SSR(1:0) = 01<br>SSR(1:0) = 10                                                                                                     | 5<br>30                   |      | 40<br>140              | ns<br>ns             |

| 508         | Ri()cal      | Source Impedance                                     | With calibration modes                                                                                                                                   |                           | 2.5  | 4                      | kΩ                   |

| 509         | l()cal       | Permissible Load Current                             | With calibration modes                                                                                                                                   | -3                        |      | 3                      | μA                   |

| 510         | llk()        | Leakage Current with Reversed<br>Supply Voltage      |                                                                                                                                                          |                           |      | 100                    | μA                   |

| 511         | MTD()        | Min. Phase Distance Tolerance                        | referred to nominal value                                                                                                                                | -25                       |      | +25                    | %                    |

| Contr       | olled Powe   | r Supply: PWR                                        |                                                                                                                                                          |                           |      |                        |                      |

| 601         | Vs()hi       | Saturation Voltage hi                                | Vs() = VDD - V();<br>ADJ(8:0) = 0x19F, I() = -5 mA<br>ADJ(8:0) = 0x1BF, I() = -10 mA<br>ADJ(8:0) = 0x1DF, I() = -25 mA<br>ADJ(8:0) = 0x1FF, I() = -40 mA |                           |      | 1<br>1<br>1<br>1.2     | V<br>V<br>V<br>V     |

| 602         | Isc()hi      | Short-Circuit Current hi                             | V(PWR) = 0VDD - 1 V;<br>ADJ(8:0) = 0x19F<br>ADJ(8:0) = 0x1BF<br>ADJ(8:0) = 0x1DF<br>V(PWR) = 0VDD - 1.2 V;<br>ADJ(8:0) = 0x1FF                           | -10<br>-20<br>-50<br>-100 |      | -4<br>-8<br>-20<br>-40 | mA<br>mA<br>mA<br>mA |

| Bias (      | Current So   | urce and Reference Voltages                          |                                                                                                                                                          |                           |      |                        |                      |

| 801         | VBG          | Bandgap Reference Voltage                            |                                                                                                                                                          | 1.2                       | 1.25 | 1.3                    | V                    |

| 802         | VPAH         | Reference Voltage Source                             |                                                                                                                                                          | 45                        | 50   | 55                     | %VDDS                |

| 803         | VOSref       | S/C a. Z Offset Cal. Reference<br>Voltage Source     |                                                                                                                                                          | 450                       | 500  | 550                    | mV                   |

| 804         | IBN          | Bias Current Source                                  | CFGIBN = 0x0<br>CFGIBN = 0xF<br>calibrated at Ta = 25 °C                                                                                                 | 110<br>180                | 200  | 370<br>220             | μΑ<br>μΑ<br>μΑ       |

Rev C1, Page 6/20

## **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol      | Parameter                                                   | Conditions                                   | Min.         | Тур.   | Max.      | Unit     |

|-------------|-------------|-------------------------------------------------------------|----------------------------------------------|--------------|--------|-----------|----------|

| Alarm       | Message C   | Dutput: NERR                                                | 1                                            |              |        |           |          |

| B01         | Vs()lo      | Saturation Voltage lo                                       | Versus GND; I() = 4 mA                       |              |        | 0.4       | V        |

| B02         | lsc()lo     | Short-Circuit Current lo                                    | Versus GND; V(NERR) ≤ VDD<br>V(NERR) > VTMon |              | 5<br>2 | 7         | mA<br>mA |

| B03         | lpu()       | Pull-Up Current Source                                      | V() = 0VDD - 1 V; EPU = 1                    | -400         | -300   | -200      | μA       |

| B04         | VTMon       | TMon Setup Preparation Threshold Increasing voltage at NERR |                                              |              |        | VDD<br>+2 | V<br>V   |

| B05         | VTMoff      | Setup Trigger Threshold                                     | Decreasing voltage at NERR                   | VDD +<br>0.5 |        |           | V        |

| B06         | VTMhys      | Setup Trigger Threshold Hystere-<br>sis                     | VTMhys = VTMon - VTMoff                      | 0.15         | 0.3    |           | V        |

| B07         | dt(NERR)lc  | Alarm Indication Time Tolerance                             | Nominal time see table 40                    | -25          |        | +25       | %        |

| Suppl       | y Switch an | d Reverse Polarity Protection: V                            | DDS, GNDS                                    |              |        |           |          |

| C01         | Vs()        | Saturation Voltage VDDS vs.<br>VDD                          | Vs() = VDD - V(VDSS); I(VDDS) = -20 mA       |              |        | 250       | mV       |

| C02         | Vs()        | Saturation Voltage GNDS vs.<br>GNS                          | Vs() = V(GNDS) - GND; I(GNDS) = 20 mA        |              |        | 250       | mV       |

| C03         | I(VDD)rev   | Supply Current in VDD with Reverse Polarity                 |                                              | -1           |        | 0         | mA       |

| Serial      | EEPROM In   | nterface: SDA, SCL                                          |                                              |              |        |           |          |

| D01         | Vs()lo      | Saturation Voltage lo                                       | I() = 4 mA                                   |              |        | 400       | mV       |

| D02         | lsc()       | Short-Circuit Current lo                                    |                                              | 4            |        | 75        | mA       |

| D03         | Vt()hi      | Input Threshold Voltage hi                                  |                                              |              |        | 2         | V        |

| D04         | Vt()lo      | Input Threshold Voltage lo                                  |                                              | 0.8          |        |           | V        |

| D05         | Vt()hys     | Input Threshold Hysteresis                                  | Vt()hys = Vt()hi - Vt()lo                    | 300          | 500    |           | mV       |

| D06         | lpu()       | Input Pull-Up Current                                       | V() = 0VDDS - 1 V                            | -600         | -300   | -60       | μA       |

| D07         | Vpu()       | Input Pull-Up Voltage                                       | V() = VDDS - V(); I() = -5 µA                |              |        | 0.4       | V        |

| D08         | f(SCL)      | Clock Frequency SCL                                         |                                              | 60           | 80     | 100       | kHz      |

| D09         | tbusy()cfg  | Configuration Sequence                                      | Single reading sequence                      |              | 18     | 24        | ms       |

| Temp        | erature Mon |                                                             |                                              |              |        |           |          |

| E01         | Toff        | Shutdown Temperature                                        |                                              |              | 155    |           | °C       |

| E02         | Thys        | Shutdown Temperature Hystere-<br>sis                        |                                              |              | 30     |           | °C       |

Rev C1, Page 7/20

## **DEVICE SETUP**

| <b>M Interface</b> Page 10<br>Device ID of the EEPROM providing the<br>chip configuration data (e.g. 0x50)                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (address range 0x00 to 0x2E)                                                                                                                                                                                                        |

| <b>Source</b> Page 11<br>Bias Trimming                                                                                                                                                                                              |

| odes Page 11<br>Mode select                                                                                                                                                                                                         |

| Irations                                                                                                                                                                                                                            |

| Bias Voltage, S/C Channel<br>I/V Mode and Input Resistance,<br>Z Channel                                                                                                                                                            |

| Bias Voltage, Z Channel                                                                                                                                                                                                             |

| thPage 13S/C Channel Gain RangeGain Factor SineGain Factor CosineOffset Range SineOffset Range CosineOffset Factor SineOffset Factor CosineS/C Channel Offset Reference SourceIntermediate Voltage SineS/C Channel Phase Correction |

|                                                                                                                                                                                                                                     |

| Controlled P  | ower Supply Page 16                   |

|---------------|---------------------------------------|

| ADJ:          | PWR output adjustment                 |

| Z Signal Pat  | h Page 15                             |

| GRZ:          | Z Channel Gain Range                  |

| GFZ:          | Gain Factor Zero                      |

| ORZ:          | Offset Range Zero                     |

| OFZ:          | Offset Factor Zero                    |

| VOSZ:         | Z Channel Offset Reference Source     |

| Zero Signal   | SetupPage 17                          |

| CFGZ:         | Zero Signal Logic                     |

| CFGZPOS:      | Zero Signal Positioning               |

| Sine-to-Digit | al Conversion Page 16                 |

| SELRES:       | Resolution                            |

| SELHYS:       | Hysteresis                            |

| Output Setti  | ngsPage 17                            |

| MTD:          | Minimum Phase Distance                |

| SSR:          | Slew Rate                             |

| TRIHL:        | Drive Mode                            |

| Error Monito  | oring and Alarm Output Page 18        |

| EMTD:         | Minimal Alarm Indication Time         |

| EPH:          | Alarm Output Logic                    |

| EPU:          | Alarm Output Pull-Up Enable           |

| EMASKA:       | Error Event Mask for Alarm Indication |

| EMASKO:       | Error Event Mask for Driver Shutdown  |

Rev C1, Page 8/20

| Registe  | er Map          |                |               |           |                                      |           |           |                           |

|----------|-----------------|----------------|---------------|-----------|--------------------------------------|-----------|-----------|---------------------------|

| Adr      | Bit 7           | Bit 6          | Bit 5         | Bit 4     | Bit 3                                | Bit 2     | Bit 1     | Bit 0                     |

| Serial E | EPROM Interf    | ace            | 1             |           | 1                                    |           |           |                           |

| 0x00     | 0               |                |               |           | DEVID(6:0)                           |           |           |                           |

| Bias Cu  | rrent Source    | 1              |               |           |                                      |           |           |                           |

| 0x01     |                 | CFGIE          | 3N(3:0)       |           | 0                                    | 0         | 0         | 0                         |

| Operati  | ng Modes        |                |               |           | 1                                    | 1         |           | 1                         |

| 0x02     | 0               | 1              | 1             | 0         |                                      | MOD       | E(3:0)    |                           |

| Input Co | onfigurations   |                |               |           |                                      |           |           |                           |

| 0x03     | 0               | 0              | 0             | 0         | 0                                    | INMODE    | 1         | 1                         |

| S/C Sig  | nal Path, Inpu  | t Configuratio | n             | I         | 1                                    | I         |           | I                         |

| 0x04     |                 | -              | GFC(4:0)      |           |                                      |           | GRSC(2:0) |                           |

| 0x05     |                 | GFS            | 6(3:0)        |           | 0                                    | 0         | 0         | 0                         |

| 0x06     | VDCS(0)         | 0              | 0             | 0         | 0                                    |           | GFS(6:4)  |                           |

| 0x07     | 0               | 0              | 0             |           |                                      | VDCS(5:1) |           |                           |

| 0x08     | ORS(0)          |                |               | VDC       | C(5:0)                               |           |           | 0                         |

| 0x09     |                 | OFS            | 6(3:0)        |           | 0                                    | 0         | 0         | ORS(1)                    |

| 0x0A     | 0               | 0              | ORC           | C(1:0)    |                                      | OFS       | 8(7:4)    |                           |

| 0x0B     |                 |                |               | OFC(6:0)  |                                      |           |           | 0                         |

| 0x0C     |                 | PHSC(2:0)      |               | 0         | 0                                    | 0         | 0         | OFC(7)                    |

| 0x0D     | 0               | 0              | 0             | 1         | 1                                    |           | PHSC(5:3) |                           |

| 0x0E     | 1               | BIASSC         | VOSS          | C(1:0)    |                                      | RSC       | 2(3:0)    |                           |

| Control  | led Power Su    | oply           | T             | I         | T                                    | 1         | T         | 1                         |

| 0x0F     | ADJ(0)          | 0              | 0             | 0         | 1                                    | 0         | 0         | 0                         |

| 0x10     |                 |                |               | ADJ       | (8:1)                                |           |           |                           |

| Z Signa  | I Path, Input C | Configuration  |               |           |                                      |           |           |                           |

| 0x11     |                 |                | GFZ(4:0)      |           |                                      |           | GRZ(2:0)  |                           |

| 0x12     |                 | 1              |               | (5:0)     | ORZ(1:0)                             |           |           |                           |

| 0x13     | 0               | BIASZ          | VOSZ          | Z(1:0)    | RZ(3:0)                              |           |           |                           |

| Error M  | onitoring       |                |               |           |                                      |           |           |                           |

| 0x14     |                 | 1              |               |           | KA(7:0)                              |           | T         |                           |

| 0x15     | 1               | 0              |               | EMTD(2:0) |                                      | EPH       | EMAS      | <a(9:8)< td=""></a(9:8)<> |

| 0x16     |                 | 1              |               |           | <b>≺O</b> (7:0)                      |           | <b></b>   |                           |

| 0x17     | 0               | 0              | 0             | 0         | 0                                    | EPU       |           | <o(9:8)< td=""></o(9:8)<> |

| 0x18     | 0               | 0              | 0             | 0         | 0                                    | 0         | 0         | 0                         |

| -        | gnal Setup      |                | -             |           |                                      | 050       | 7(0.0)    |                           |

| 0x19     | 0               | 0              | 0             |           | 00(7:0)                              | CFG       | Z(3:0)    |                           |

| 0x1A     |                 |                |               |           | OS(7:0)                              |           |           |                           |

|          | Digital Conve   | rsion, Minimu  | Im Phase Dist |           | $\mathbf{D}(\mathbf{Z}, \mathbf{n})$ |           |           |                           |

| 0x1B     |                 | 1              |               |           | ES(7:0)                              |           |           |                           |

| 0x1C     | 0               |                | (2.0)         | ,         | SELRES(14:8                          | ,         |           |                           |

| 0x1D     |                 | IVITL          | 0(3:0)        |           |                                      | SELH      | YS(3:0)   |                           |

| -        | Settings        |                |               |           | 005                                  | (4.0)     |           | (4.0)                     |

| 0x1E     | 0               | 0              | 1             | 0         | SSR                                  | (1:0)     | I KIH     | L(1:0)                    |

Rev C1, Page 9/20

| Registe | r Map                                                       |         |               |                |                 |                   |       |       |  |  |

|---------|-------------------------------------------------------------|---------|---------------|----------------|-----------------|-------------------|-------|-------|--|--|

| Adr     | Bit 7                                                       | Bit 6   | Bit 5         | Bit 4          | Bit 3           | Bit 2             | Bit 1 | Bit 0 |  |  |

| Reserve | d Memory Se                                                 | ction 1 |               |                |                 |                   |       | 1     |  |  |

| 0x1F    | Internal use only; keep all bits at zero for initialization |         |               |                |                 |                   |       |       |  |  |

| 0x20    | Internal use only; keep all bits at zero for initialization |         |               |                |                 |                   |       |       |  |  |

| Reserve | d Memory Se                                                 | ction 2 |               |                |                 |                   |       |       |  |  |

| 0x21    | 0                                                           | 0       | 0             | 0              | 1               | 0                 | 0     | 0     |  |  |

| 0x22    |                                                             |         | nternal use c | only; keep all | bits at zero fo | or initialization | ו     | •     |  |  |

| 0x23    |                                                             |         | nternal use c | only; keep all | bits at zero fo | or initializatior | ו     |       |  |  |

| 0x24    |                                                             |         |               | • •            | ecific OEM da   |                   |       |       |  |  |

| 0x25    |                                                             |         | Ap            | oplication-spe | ecific OEM da   | ata               |       |       |  |  |

| 0x26    |                                                             |         |               | · ·            | ecific OEM da   |                   |       |       |  |  |

| 0x27    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x28    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x29    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x2A    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x2B    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x2C    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x2D    |                                                             |         |               |                | ecific OEM da   |                   |       |       |  |  |

| 0x2E    |                                                             |         | Ap            | oplication-spe | ecific OEM da   | ata               |       |       |  |  |

| CRC Dat | а                                                           |         |               |                |                 |                   |       |       |  |  |

| 0x2F    |                                                             |         |               | CHKSI          | JM(7:0)         |                   |       |       |  |  |

| Reserve | d Memory Se                                                 | ction 3 |               |                |                 |                   |       |       |  |  |

| 0x30    |                                                             |         | nternal use c | only; keep all | bits at zero fo | or initializatior | l     |       |  |  |

| 0x31    |                                                             |         |               | • •            | bits at zero fo |                   |       |       |  |  |

| 0x32    | Internal use only; keep all bits at zero for initialization |         |               |                |                 |                   |       |       |  |  |

| 0x33    |                                                             |         | nternal use c | only; keep all | bits at zero fo | or initializatior | ו     |       |  |  |

| Notes   |                                                             | AI      | 0 and 1 entr  | ries are mano  | datory for dev  | ice initializati  | on    |       |  |  |

Table 4: Register Map

Rev C1, Page 10/20

Haus

#### SERIAL EEPROM INTERFACE

The serial configuration interface consists of the two pins SCL and SDA and enables read access to a serial EEPROM (requirements: 1 Kbit, 128x8,  $3.3 \vee$  to  $5 \vee$  operation, device address 0x50 "1010 000"; recommended: Atmel AT24C01B; notes: devices ignoring A2...0 address bit settings are not suitable).

Once the supply has been switched on (power down reset) iC-MG reads the configuration from the EEP-ROM which has the device ID 0x50. Bit errors in the 0x00 to 0x2F memory area are monitored by the CRC deposited in register CHKSUM (see program example; the polynomial used is "1 0001 1101"). Should an error occur while the data is being read in the readin process is repeated; the system aborts following a fourth faulty attempt and tristates the output drivers.

As an alternative to the power down reset iC-MG can be triggered to again read in the configuration via pin NERR. To this end pin voltage V(NERR) must initially exceed threshold voltage VTMon (see Electrical Characteristics). Once the pin voltage has dropped to below VTMon iC-MG starts communicating with the EEP-ROM. The device ID stored in register DEVID is used to address the EEPROM.

iC

#### **Example of CRC Calculation Routine**

```

unsigned char ucDataStream = 0;

int iCRCPoly = 0x11D;

unsigned char ucCRC=0;

int i = 0;

ucCRC = 1; // start value !!!

for (iReg = 0; iReg<47; iReg ++) {

ucDataStream = ucGetValue(iReg);

for (i=0; i<=7; i++) {

if ((ucCRC & 0x80) != (ucDataStream & 0x80))

ucCRC = (ucCRC << 1) ^ iCRCPoly;

else

ucCRC = (ucCRC << 1);

ucDataStream = ucDataStream << 1;

}

}

```

Rev C1, Page 11/20

#### **OPERATING MODES**

| MODE | Adr 0x02, bit 3:0                                         |                |                |                |                |                 |        |      |

|------|-----------------------------------------------------------|----------------|----------------|----------------|----------------|-----------------|--------|------|

| Code | Operating Mode                                            | Pin A          | Pin NA         | Pin B          | Pin NB         | Pin Z           | Pin NZ | NERR |

| 0x00 | ABZ Mode                                                  | A              | NA             | В              | NB             | Z               | NZ     | NERR |

| 0x01 | Calibration Mode 1                                        |                | VREFIZ         | VREFISC        | IBN            | PCH-Z           | NCH-Z  |      |

| 0x02 | Calibration Mode 2                                        | PCH-S          | NCH-S          | PCH-C          | NCH-C          | VDCS            | VDCC   |      |

| 0x0B | System Test Mode *                                        | A <sub>4</sub> | A <sub>8</sub> | B <sub>4</sub> | B <sub>8</sub> | Z <sub>In</sub> |        | NERR |

|      | * Note: Setting SELRES=0x132 and SELHYS=0xF is mandatory. |                |                |                |                |                 |        |      |

Table 5: Operating Modes

iC-MG has several modes of operation which are set via MODE. In addition to the primary operational mode *ABZ Mode* for the output of encoder quadrature signals via differential line drivers both analog and digital calibration signals can be selected which can be used to set up the integrated signal conditioning unit.

#### ABZ Mode

In *ABZ Mode* complementary signals are always output. Here, converter setting SELRES determines the A/B pulse count and zero signal settings CFGZ and CFGPOS the width and position of the generated zero signal (dependent on an enable from  $Z_{ln}$ ).

#### Calibration Mode 1, Mode 2

So that signal amplitudes and offset voltages can be calibrated internal analog signals are switched to the output pins directly and the digital line drivers shut down. Due to internal resistances of up to  $4 \text{ k}\Omega$  a high-impedance measurement is advisable.

In *Calibration Mode 1* bias current source IBN and the internal zero signal are available after the input amplifier (signals PCH-Z and NCH-Z). The calibration of IBN is described on page 11, that of the zero signal on page 15.

**BIAS CURRENT SOURCE CALIBRATION**

The calibration of the bias current source is prerequisite for adherence to the given electrical characteristics and also instrumental in the determination of the chip timing (e.g. the minimum phase distance and SCL clock frequency). For setup purposes *Calibration Mode 1* is activated and the IBN current measured using a  $10 \text{ k}\Omega$  resistor switched to VDDS. The setpoint is 200 µA which is equivalent to a measurement voltage of 2 V.

In *Calibration Mode 2* the conditioned sine and cosine signals are output (signals PCH-S, NCH-S, PCH-C and NCH-C). Additionally, the intermediate potentials of both input channels are also available, with VDCS for the sine and VDCC for the cosine channel. The calibration of these intermediate voltages is described on page 14.

#### System Test Mode

*System Test Mode* permits the fine adjustment of the sine and cosine input signals using digital signals. The registers mentioned above must also be set for this mode.

The  $A_4$  duty cycle acts as a measure for the offset of the sine channel, with the  $B_4$  duty cycle a measure for that of the cosine channel. The duty cycle at  $A_8$  represents the phase error between sine and cosine or any deviation from the ideal value of 90°. The calibration of differing signal amplitudes enables the duty cycle at  $B_8$ . A duty cycle of 50 % is the calibration target for all digital test signals.

Signal Z<sub>In</sub> is the unmasked digitized zero signal.

| CFGIBN | Adr 0x01, bit 7:4          |        |                           |

|--------|----------------------------|--------|---------------------------|

| Code k | $IBN \sim \frac{31}{39-k}$ | Code k | $IBN \sim rac{31}{39-k}$ |

| 0x0    | 79%                        | 0x8    | 100 %                     |

| 0x1    | 81 %                       | 0x9    | 103 %                     |

| 0x2    | 84%                        | 0xA    | 107 %                     |

| 0x3    | 86 %                       | 0xB    | 111 %                     |

| 0x4    | 88 %                       | 0xC    | 115 %                     |

| 0x5    | 91 %                       | 0xD    | 119%                      |

| 0x6    | 94%                        | 0xE    | 124 %                     |

| 0x7    | 97 %                       | 0xF    | 129%                      |

Table 6: Bias Current Source Calibration

Rev C1, Page 12/20

f Haus

#### INPUT CONFIGURATIONS

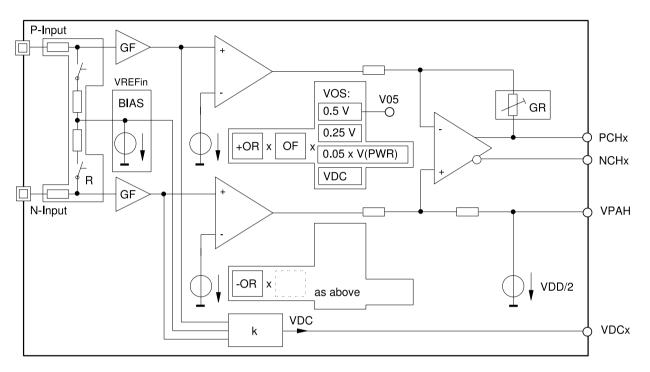

Figure 1: Input instrumentation amplifier and signal conditioning

All input stages are configured as instrumentation amplifiers and thus directly suitable for differential input signals. Referenced input signals can be processed as required; in Single-Ended Input Mode the NZERO input acts as a reference, replacing the input signals from NSIN and NCOS.

| INMODE | Adr 0x03, bit 2                            |

|--------|--------------------------------------------|

| 0      | Differential input signals                 |

| 1      | Single-ended input signals *               |

| Note   | * Input NZERO is reference for all inputs. |

Table 7: Input Signal Mode

Both current and voltage signals can be processed as input signals, selected by RSC(0) and RZ(0). In I Mode an input resistor Rin() becomes active at each input pin, converting the current signal into a voltage signal. The input resistance Rin() consists of a pad wiring resistor and resistor Rui() which is linked to the adjustable bias voltage source VREFin(). The following table shows the possible selections, with Rin() giving the typical resulting input resistance (see Electrical Characteristics for tolerances).

The input resistor should be set in such a way that intermediate potentials VDCS and VDCC lie between

125 mV and 250 mV (verifiable in Calibration Mode 2). In V Mode an optional voltage divider can be selected which reduces unacceptably large input amplitudes to ca. 25%. The circuitry is equivalent to the resistor chain in I Mode; the pad wiring resistor is considerably larger here, however.

| RSC  | Adr 0x0E, bit 3:0 |                |               |  |

|------|-------------------|----------------|---------------|--|

| RZ   | Adr 0x13, bit 3:0 |                |               |  |

| Code | Nominal Rin()     | Internal Rui() | I/V Mode      |  |

| -000 | 1.7 kΩ            | 1.6 kΩ         | Current input |  |

| -010 | 2.5 kΩ            | 2.3 kΩ         | Current input |  |

| -100 | 3.5 kΩ            | 3.2 kΩ         | Current input |  |

| -110 | 4.9 kΩ            | 4.6 kΩ         | Current input |  |

| 1—1  | 20 kΩ             | 5 kΩ           | Voltage input |  |

| 0—1  | high<br>impedance | 1 ΜΩ           | Voltage input |  |

Table 8: I/V Mode and Input Resistance

| BIASSC | Adr 0x0E, bit 6 |                                  |

|--------|-----------------|----------------------------------|

| BIASZ  | Adr 0x13, bit 6 |                                  |

| Code   | VREFin()        | Type of sensor                   |

| 0      | 2.5 V           | Lowside current sink (I Mode)    |

| 1      | 1.5 V           | Highside current source (I Mode) |

Table 9: Input Bias Voltage

#### Rev C1, Page 13/20

**fH**aus

#### S/C SIGNAL PATH and CALIBRATION

The analog voltage signals needed to calibrate the sine signals can be measured in *Calibration Mode 2*. The characteristic digital parameters for offset, amplitude and phase errors can be measured in *System Test Mode*.

#### S/C Gain Settings

The gain is set in four stages:

1. The sensor supply tracking is shut down and the constant current source for the PWR output set to a suitable output current (register ADJ; current value close to the later operating point).

2. The coarse gain is selected so that differential signal amplitudes of ca. 1 Vpp are produced internally (signal PCHx vs. NCHx for the sine or cosine channel).

3. Using fine gain factor GFC the cosine signal amplitude is then adjusted to 1 Vpp.

4. The sine signal amplitude can then be calibrated to the cosine signal amplitude via fine gain factor GFS.

| GRSC | Adr 0x04, bit 2:0  |                    |

|------|--------------------|--------------------|

| Code | Range with RSC=0x9 | Range with RSC≠0x9 |

| 0x0  | 0.5                | 2.0                |

| 0x1  | 1.0                | 4.1                |

| 0x2  | 1.3                | 5.3                |

| 0x3  | 1.7                | 6.7                |

| 0x4  | 2.2                | 8.7                |

| 0x5  | 2.6                | 10.5               |

| 0x6  | 3.3                | 13.2               |

| 0x7  | 4.0                | 16.0               |

#### Table 10: S/C-Channel Gain Range

| GFC  | Adr 0x04, bit 7:3                   |

|------|-------------------------------------|

| Code | Factor                              |

| 0x00 | 1.00                                |

| 0x01 | 1.06                                |

|      | 6.25 <sup>GFC</sup> / <sub>31</sub> |

| 0x1F | 6.25                                |

#### Table 11: Gain Factor Cosine

| GFS  | Adr 0x06, bit 2:0, Adr 0x05, bit 7:4 |

|------|--------------------------------------|

| Code | Factor                               |

| 0x00 | 1.0                                  |

| 0x01 | 1.015                                |

|      | 6.25 <sup>GFS</sup> / <sub>124</sub> |

| 0x7F | 6.53                                 |

Table 12: Gain Factor Sine

#### S/C Offset Calibration

To calibrate the offset the reference source must first be selected using VOSSC. Two fixed voltages and two dependent sources are available for this purpose. The fixed voltage sources should be selected for external sensors which already provide stable, self-regulating signals.

For the operation of photosensors in optical encoders, iC-MG tracks changes in offset voltages via the signaldependent source VDC when used in conjunction with the controlled power supply output supplying the encoder LED (pin PWR). The VDC potential automatically tracks higher DC photocurrents. To this end intermediate potentials VDCS and VDCC must be adjusted to a minimal AC ripple using the selectable k factor (this calibration must be repeated when the gain setting is altered). The ideal DC voltage level of 0.25 V to 0.5 V is selected via the input resistor Rui().

The feedback of pin voltage V(PWR) fulfills the same task as source VDC when MR bridge sensors are supplied by the controlled power supply output. In this instance the VDC sources do not need adjusting.

| VOSSC | Adr 0x0E, bit 5:4    |

|-------|----------------------|

| Code  | Type of source       |

| 0x0   | 0.05 · V(PWR)        |

| 0x1   | 0.5 V                |

| 0x2   | 0.25 V               |

| 0x3   | VDC (ie. VDCS, VDCC) |

Table 13: S/C-Channel Offset Reference Source

| VDCS | Adr 0x07, bit 4:0; Adr 0x06, bit 7                  |

|------|-----------------------------------------------------|

| VDCC | Adr 0x08, bit 6:1                                   |

| Code | $VDC = k \cdot V(P - ln) + (1 - k) \cdot V(N - ln)$ |

| 0x00 | k = 0.33                                            |

| 0x01 | k = 0.335                                           |

|      |                                                     |

| 0x3F | k = 0.66                                            |

Table 14: S/C-Channel Intermediate Voltages

Rev C1, Page 14/20

The calibration range for the S/C offset is dependent on the selected VOSSC source and is set using ORS and ORC. Both sine and cosine signals are then calibrated using factors OFS and OFC. The calibration target is reached when the DC fraction of the differential signals PCHx versus NCHx is zero.

| ORS  | Adr 0x09, bit 0; Adr 0x08, bit 7 |

|------|----------------------------------|

| ORC  | Adr 0x0A, bit 5:4                |

| Code | Range                            |

| 00   | x2                               |

| 01   | x4                               |

| 10   | x12                              |

| 11   | x24                              |

#### Table 15: S/C-Channel Offset Range

| OFS  | Adr 0xA, bit 3:0; Adr 0x9, bit 7:4 |  |  |  |

|------|------------------------------------|--|--|--|

| OFC  | Adr 0xC, bit 0; Adr 0xB, bit 7:1   |  |  |  |

| Code | Factor Code Factor                 |  |  |  |

| 0x00 | 0 0x00 0                           |  |  |  |

| 0x01 | 0.0079 0x01 -0.0079                |  |  |  |

|      |                                    |  |  |  |

| 0x7F | 1 0xFF -1                          |  |  |  |

Table 16: S/C-Channel Offset Factors

#### S/C Phase Correction

If the phase shift between the sine and cosine signal deviates from the ideal 90° this can be compensated for using parameter PHSC. Following this the calibration of the amplitude compensation, intermediate potentials and offset voltages may have to be corrected.

| PHSC | Adr 0xD, bit 2:0; Adr 0xC, bit 7:5 |      |                  |

|------|------------------------------------|------|------------------|

| Code | Correction angle                   | Code | Correction angle |

| 0x00 | +0°                                | 0x20 | - 0 °            |

| 0x01 | +0.63°                             | 0x21 | - 0.63 °         |

|      |                                    |      |                  |

| 0x1F | +20.2°                             | 0x3F | - 20.2 °         |

Table 17: Phase Correction

Rev C1, Page 15/20

Haus

#### Z SIGNAL PATH and CALIBRATION

The analog voltage signals needed to calibrate the zero signal are available in *Calibration Mode 1*. In addition it is possible to check the phase position of the PZERO/NZERO enable signal in *System Test Mode*.

#### **Gain Settings**

Parallel to the conditioning process for the S/C signals the zero signal gain is also set step by step:

1. The tracking of the sensor supply is shut down and the constant current source for the PWR output set to a suitable output current (register ADJ; current value close to the later operating point).

2. Coarse gain is selected so that differential signal amplitudes of ca. 1 Vpp are generated internally (signal PCHx vs. NCHx).

3. GFC then permits fine gain adjustment to 1 Vpp.

| GRZ  | Adr 0x11, bit 2:0 |                   |

|------|-------------------|-------------------|

| Code | Range with RZ=0x9 | Range with RZ≠0x9 |

| 0x0  | 0.5               | 2.0               |

| 0x1  | 1.0               | 4.1               |

| 0x2  | 1.3               | 5.3               |

| 0x3  | 1.7               | 6.7               |

| 0x4  | 2.2               | 8.7               |

| 0x5  | 2.6               | 10.5              |

| 0x6  | 3.3               | 13.2              |

| 0x7  | 4.0               | 16.0              |

Table 18: Z-Channel Gain Range

| GFZ  | Adr 0x11, bit 7:3                   |

|------|-------------------------------------|

| Code | Factor                              |

| 0x00 | 1.00                                |

| 0x01 | 1.06                                |

|      | 6.25 <sup>GFZ</sup> / <sub>31</sub> |

| 0x1F | 6.25                                |

Table 19: Z-Channel Gain Factor

#### **Offset Calibration**

To calibrate the offset the source of supply must first be selected using VOSZ (see S/C Offset Calibration for further information). For the zero signal path the signal dependent source is VDCS.

| VOSZ | Adr 0x13, bit 5:4 |

|------|-------------------|

| Code | Type of source    |

| 0x0  | 0.05 · V(PWR)     |

| 0x1  | 0.5 V             |

| 0x2  | 0.25 V            |

| 0x3  | VDC= VDCS         |

#### Table 20: Z-Channel Offset Reference Source

| ORZ  | Adr 0x12, bit 1:0 |

|------|-------------------|

| Code | Range             |

| 00   | x2                |

| 01   | x4                |

| 10   | x12               |

| 11   | x24               |

Table 21: Z-Channel Offset Range

| OFZ  | Adr 0x12, bit 7:2 |      |        |

|------|-------------------|------|--------|

| Code | Factor            | Code | Factor |

| 0x00 | 0                 | 0x20 | 0      |

| 0x01 | 0.032             | 0x21 | -0.032 |

|      |                   |      |        |

| 0x1F | 1                 | 0x3F | -1     |

Table 22: Z-Channel Offset Factor

Rev C1, Page 16/20

Haus

#### SIGNAL LEVEL CONTROLLER

Via the controlled power supply (pin PWR) the input signal levels for the sine-to-digital converter can be kept constant regardless of temperature and aging effects by tracking the sensor supply. Alternatively, the PWR output can be used as a constant current source for adjusting the signal conditioning, for example.

ADJ(6:0) selects the desired current for the PWR output; when adjusting the signal conditioning ideally amplitudes of ca. 1 Vpp should be possible for the PCHx to NCHx signal.

| ADJ (8:7) | Adr 0x10, bit 7:6             |

|-----------|-------------------------------|

| Code      | Function                      |

| 00        | Control to sine/cosine square |

| 01        | Control to sum of sine/cosine |

| 10        | Current source                |

| 11        | Not permitted                 |

Table 23: PWR Output Operating Mode

| ADJ (6:5) | Adr 0x10, bit 5:4 |

|-----------|-------------------|

| Code      | Function          |

| 00        | 5 mA range        |

| 01        | 10 mA range       |

| 10        | 25 mA range       |

| 11        | 50 mA range       |

Table 24: PWR Output Current Source Range

#### SINE-TO-DIGITAL CONVERSION

| SELRES | Adr 0x1C, bit 6:0; Adr 0x1B, bit 7:0 |                         |                             |

|--------|--------------------------------------|-------------------------|-----------------------------|

| Code   | Angle Steps<br>(per period)          | Interpolation<br>Factor | Permiss. Input<br>Frequency |

| 0x00E0 | 4                                    | x1                      | 200 kHz                     |

| 0x01B0 | 8                                    | x2                      | 200 kHz                     |

| 0x0398 | 16                                   | x4                      | 200 kHz                     |

| 0x0414 | 20                                   | x5                      | 200 kHz                     |

| 0x090a | 40                                   | x10                     | 100 kHz                     |

| 0x1305 | 80                                   | x20                     | 50 kHz                      |

| 0x1804 | 100                                  | x25                     | 40 kHz                      |

| 0x3102 | 200                                  | x50                     | 20 kHz                      |

Table 28: Resolution of Sine-to-Digital Conversion

| ADJ (4:0) | Adr 0x10, bit 3:0; Adr 0x0F, bit 7       |

|-----------|------------------------------------------|

| Code      | Function                                 |

| 0x00      | 3.125 % of Isc(PWR)                      |

|           |                                          |

| 0x1F      | 100 % of Isc(PWR)                        |

| Note      | Settings apply with current source mode. |

iC

#### Table 25: PWR Output Short-Circuit Current

| ADJ (4:0) | Adr 0x10, bit 3:0; Adr 0x0F, bit 7                                                   |

|-----------|--------------------------------------------------------------------------------------|

| Code      | Function                                                                             |

| 0x00      | 60%                                                                                  |

|           |                                                                                      |

| 0x1A      | ca. 100%                                                                             |

|           |                                                                                      |

| 0x1F      | 120%                                                                                 |

| Note      | Settings apply with s/c square control mode.<br>Recommended entry for 1.0 V is 0x1A. |

#### Table 26: PWR Output Signal Adjustment

| ADJ (4:0) | Adr 0x10, bit 3:0; Adr 0x0F, bit 7    |

|-----------|---------------------------------------|

| Code      | Function                              |

| 0x00      | VDCS + VDCC = 224 mV                  |

|           |                                       |

| 0x1F      | VDCS + VDCC = 472 mV                  |

| Note      | Settings apply with sum control mode. |

#### Table 27: PWR Output Signal Adjustment

| SELHYS     | Adr 0x1D, bit 3:0                                   |

|------------|-----------------------------------------------------|

| Code       | Function                                            |

| 0x0 to 0x1 | Device test only                                    |

| 0x2        | 1 increment ( $\approx$ 1.8°)                       |

| 0x3 to 0xD | 1.5 to 6.5 increments ( $\approx$ 2.7°-11.7°)       |

| 0xE        | SELRES(6:1) increments, i.e. 0.5 LSB                |

| 0xF*       | SELRES(6:0) increments, i.e. 1 LSB                  |

| Note       | *Not permitted in combination with<br>SELRES=0x00E0 |

Table 29: Encoding of conversion hysteresis

The angle hysteresis is set via SELHYS in multiples of the increment size. With reference to the input sine cycle the maximum length can be 45°.

Rev C1, Page 17/20

Haus

#### **OUTPUT SETTINGS**

#### **Configuration of Output Drivers**

The output drivers can be used as push-pull, lowside or highside drivers. TRIHL(1:0) selects the mode of operation. In order to avoid steep edges during transmission via short cables the slew rate can be reduced using SSR (tolerances as given in Electrical Characteristics).

| TRIHL | Adr 0x1E, bit 1:0                           |

|-------|---------------------------------------------|

| Code  | Function                                    |

| 00    | Push-pull operation                         |

| 01    | Highside driver mode (P channel open drain) |

| 10    | Lowside driver mode (N channel open drain)  |

| 11    | Not permitted                               |

Table 30: Output Drive Mode

| SSR  | Adr 0x1E, bit 3:2                   |

|------|-------------------------------------|

| Code | Function                            |

| 01   | Nominal value 25 ns                 |

| 10   | Nominal value 80 ns                 |

| Note | Entries 00 and 11 are not permitted |

Table 31: Output Slew Rate

#### **Minimum Phase Distance**

The minimum phase distance for the A/B and Z output signals can be preselected using MTD(3:0). This setting limits the maximum possible output frequency for secure transmission to counters which are either unable to debounce noise spikes or only permit low input frequencies.

| MTD  | Adr 0x1D, bit 7:4                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------|

| Code | Function                                                                                                                       |

| 0x8  | 200 ns                                                                                                                         |

| 0x9  | 400 ns                                                                                                                         |

|      |                                                                                                                                |

| 0xE  | 1.4 µs                                                                                                                         |

| 0xF  | 1.6 µs                                                                                                                         |

| Note | Codes 0x0 to 0x7 are not permitted.<br>All timing specifications are nominal values, see<br>Elec. Char. No.511 for tolerances. |

Table 32: Minimum Phase Distance

When selecting the minimum phase distance the slew rate setting of the RS422 output drivers and the length of cable used must be taken into consideration.

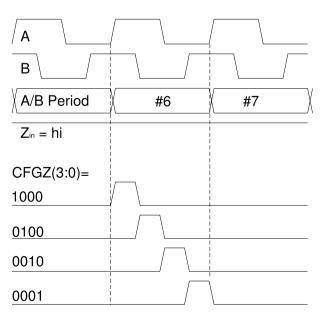

#### Zero Signal Positioning

The output of the zero pulse, generated internally, is based on an enable from  $Z_{In}$  which can be observed in *System Test Mode* and in *ABZ Mode* at pin NERR (via EMASKA= 0x010 and EMTD= 0x0). As the offset calibration of the zero signal alters the signal width the correct position and width of signal  $Z_{In}$  should be checked before the digital configuration parameters are determined.

The zero pulse output position can be selected via CFGZPOS(6:0); the cycle count begins with the sine zero crossing. No zero pulse is output for all values which are either greater than or equal to the interpolation factor.

| CFGZPOS | Adr 0x1A, bit 7:0                          |

|---------|--------------------------------------------|

| Bit     | Function                                   |

| 7       | Enables the selection below                |

| 6:0     | Count of A/B period releasing the Z output |

Table 33: Zero Signal Positioning

| CFGZ | Adr 0x19, bit 3:0            |

|------|------------------------------|

| Code | Function                     |

| 1000 | Enables Z= 1 with A= 1, B= 1 |

| 0100 | Enables Z= 1 with A= 1, B= 0 |

| 0010 | Enables Z= 1 with A= 0, B= 0 |

| 0001 | Enables Z= 1 with A= 0, B= 1 |

#### Table 34: Zero Signal Logic